PAMĚŤOVÉ FUNKCE - KLOPNÝ OBVOD (RS, SR)

Charakteristika

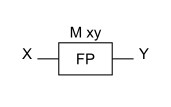

Paměťové funkce jsou určeny k trvalému nebo dočasnému zaznamenání stavu, který byl definován signálem krátkého trvání - impulsem, například tlačítkové ovládání

zapnutí/vypnutí. Pro uchování stavu je vždy nutno určit, kde se má stav zaznamenat / uchovat, konkrétně na jakém bitu paměti, dále je tento bit paměti označován

jako M xy, kde M značí obecně paměť (memory) a xy obecné adresování bitu. U různých výrobců je toto značení a adresování různé.

|

Klopný obvod

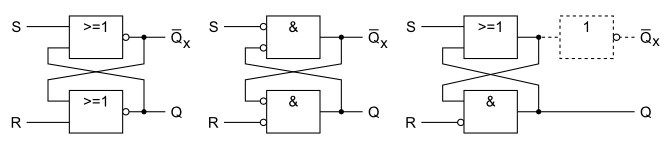

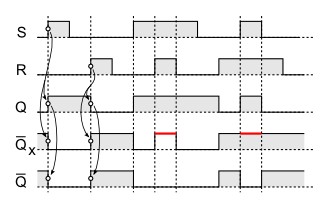

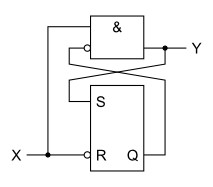

Klopný obvod je možno realizovat kombinačním zapojením jednoduchých logických funkcí AND, OR, NOT s využitím zpětné vazby. Pro řízení klopného obvodu se používají

vstupy S (set), tedy nastavení výstupního signálu Q na hodnotu Log. 1 a vstup R (reset), který nastaví výstupní signál Q na hodnotu

Log. 0. Samotné takovéto

řešení klopného obvodu (pomocí logických funkcí) není v PLC zakázané ale výrobci PLC poskytují instrukce a bloky pro realizaci klopného obvodu jednodušším způsobem.

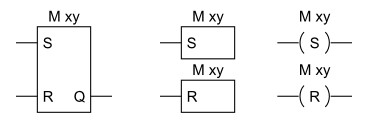

Jedním ze způsobů je případ, kdy výrobce v grafickém zobrazení poskytuje blok, který má dva řídící vstupy S a R a výstup Q. Tento

blok je vhodný pro případ, kdy zapojení logiky (AND, OR, ...) na vstupech není příliš rozsáhlé z hlediska prostoru pro grafické zobrazení. Z hlediska správné

a definované funkce klopného obvodu je problematický případ, kdy jsou oba vstupy S i R ve stavu Log.1. Podle způsobu realizace klopného obvodu mohou nastat dále uvedené dva případy,

které se liší priorizací vstupu S nebo R, podle toho jaký stav má zaujmout výstup Q při současném stavu Log.1 na obou vstupech S a R.

Druhý způsob je použití samostatného S nastavení výstupu Q a samostatného resetování R výstupu Q. Toto pak může být provedeno v

různých částech nebo místech programu i když se tím mírně ztrácí přehlednost. Při samostatném použití S a R není vyloučen ani zakázán případ,

kdy jsou tyto příkazy / instrukce použity opakovaně, je však třeba mít na paměti, že stav Q se může měnit při každém průchodu instrukcí S

nebo R a dotazování na výstup Q před zpracováním poslední instrukce S / R může poskytovat nedefinovaný stav výstupu Q. Zde

platí, že prioritní je ta instrukce (vstup, funkce) S / R, která je zpracována jako poslední.

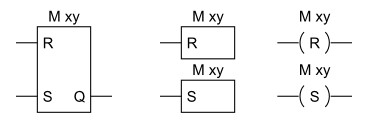

Klopný obvod SR

Klopný obvod RS

|

Detekce hrany signálu

Detekce hrany signálu je častým požadavkem při řízení systémů, jedná se o případ, kdy má být daná operace řízení provedena pouze jednou, právě při

změně stavu sledovaného (řídícího) signálu, podle požadavku na náběžnou nebo sestupnou hranu signálu. Systémový SW moderní PLC již obsahuje funkce, dodávané

výrobcem, které řeší tuto problematiku a postačí pouze definovat paměťový bit pro uchování předchozího stavu.

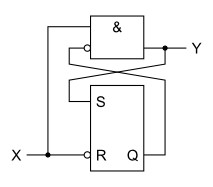

Pokud taková funkce není v systému k dispozici (například starší CPU), je možno takovou funkci řešit vlastním programem. Protože detekce hrany signálu vyžaduje,

aby byl znám předchozí stav signálu (v předchozím cyklu CPU) je nutno použít nějaký typ paměťové funkce, realizovaný jako

RS klopný obvod v potřebném logickém zapojení s dalšími logickými členy. Takovéto řešení ale vyžaduje dva pomocné paměťové bity, jeden pro uchování předchozího

stavu a jeden pro přenos signálu (může se lišit podle podpory vývojového prostředí). Toto klasické řešení zpravidla vyžaduje 7 instrukcí programu, stejné

funkce lze ale dosáhnout i s 5 instrukcemi programu.

| Popis: |

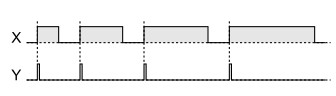

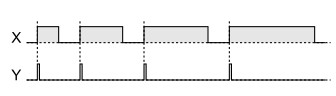

Funkce (nebo zapojení) generuje impuls na výstupu Y (stav Log.1) v případě, že dojde ke změně vstupního signálu X ze stavu Log.0 na stav

Log.1. Doba trvání impulsu na výstupu Y je jeden cyklus zpracování programu v CPU.

|

| |

|

| Pravdivostní tabulka: |

| X |

Y |

| 0 |

0 |

| 0=>1 |

1 |

| 1 |

0 |

| 1=>0 |

0 |

|

| |

|

| Grafická značka: |

|

| |

|

Náhradní schéma:

(s členy NOT, AND, SR) |

|

| |

|

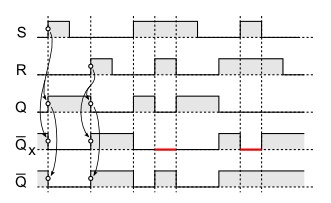

Časový diagram:

(v cyklu) |

Svislé časové dělení odpovídá jednomu cyklu zpracování programu v CPU,

tedy signál Y je krátkým impulsem v délce trvání právě doby cyklu ! |

| |

|

Časový diagram:

(obecný) |

|

| |

|

| Poznámka: |

Pokud systémová funkce obsahuje pouze funkci detekci náběžné hrany, detekci sestupné hrany je možno vytvořit pouhou negací

vstupního signálu. |

Poznámka:

Pokud systémové prostředky poskytují funkci pro detekci signálu, kdy se v jedné funkci vyhodnocuje hrana pouze jednoho signálu a nebo neposkytují-li vůbec a potřebujeme-li

detekovat hrany například na 8/16/32 signálech, je potřeba tuto funkci naprogramovat taktéž 8x/16x/32x a přiřadit jím 8/16/32 paměťových bitů pro pro uchování

předchozího stavu. Zkušený programátor však dokáže toto řešit s využitím funkcí XORB/XORW/XORD a MOVE aplikované na Byte, Word, Double Word, kdy je počet

instrukcí programu nižší než při použití samostatných instrukcí detekce hrany; počet potřebných pomocných paměťových bitů je ale nutno zachovat.

|

Ostatní klopné obvody

V praxi se vyskytují požadavky na klopné obvody řízené uvolňovacím signálem, synchronizované hodinovým impulsem, posuvné registry, děličky a další,

které využívají paměťové funkce i detekci hrany.

Tyto

klopné obvody je možno realizovat vhodným doplněním logických členů na (před) vstupy S/R, případně propojit několik SR nebo RS klopných obvodů do kaskády. V

případě složitějších požadavků jako posuvných registrů je možno využít přímo funkcí nebo instrukcí pro posunutí nebo rotaci v rámci Byte, Word, Double Word nebo pro

programově realizované děličky frekvence využít čítače.

|